Materiales semiconductores

Con la invención de un amplificador de Estado Sólido en 1947, por Shockley, Bardeen, and Brattain, la posibilidad del aumento en la integración en el mismo cristal es una realidad. En las últimas décadas, y hoy en día se aumenta el numero de componentes que se introducen en el mismo cristal. Esta industria es altamente rentable, pero las inversiones en desarrollo son también muy altas, lo que hace que las inversiones sean a la largo plazo. Lo que hace que la industria microelectrónica sea rentable es que su procesos de fabricación (Batch Processing), funcione correctamente. Esto hace que en cada chip sea de 8mm de lado, que hace que en cada oblea tengamos de 120-130 circuitos. Cada oblea es tratada de forma que todos los circuitos se hacen a la vez, pasando por el mismo proceso en el mismo instante. Aunque hay procesos como el encapsulado y el testéo, que se deben hacer individualmente.

-¿Qué semiconductores son aptos para hacer dispositivos electrónicos ?

Los elementos del tipo IV (Columna del Silicio), son los más indicados para utilizarlos como semiconductores. Aunque para que funcionen como tal deben de tener un gap comprendido, entre 0.5 y 1 eV aproximadamente. Aunque como bien se sabe ya el Gap de un semiconductor se puede variar añadiendo impurezas a este.

Pero no solo los elementos de la columna IV, son candidatos a buenos semiconductores, sino la combinación de los elementos de las columnas de al lado la III y la V, también lo son. P.e. GaAs

Ga| Ge | As

También otros dos elementos que se combinan como buenos semiconductores, es el GaP. Los elementos del grupo IV-VI, también se combinan formando semiconductores de Gap muy pequeños, pero de enorme importancia en el ámbito militar, y en la detección de infrarrojos.

P.e. PbSe (Galena)

De todas maneras, son pocos los elementos, los cuales los podemos hacer crecer como cristales.

Ahora vamos a hacer una breve historia de los dispositivos electrónicos :

1904- Primer detector de Ondas de Radio (Unión metal-PbSe)

1940-1945 Se desarrollan en Alemania. Detectores de radiación (Térmica)

Aplicación en la detección de aviones.

1547 Transistor Bipolar (Germanio)

1959 Circuitos Integrados

1961 Tecnología planar desarrollada por Fairchild Semiconductor

1963 MOSFET- Aunque la idea era anterior, por problemas tecnológicos no se pudo desarrollar ( Creación de el óxido semiconductor)

-Conceptos Industriales de Producción de CI

Custom : El fabricante lo hace todo hasta la última máscara, y los transistores con su colocación y conexión.

ASIC : Circuitos muy específicos que el fabricante no hace, por no tener asegurado un mercado (Es una relación entre cliente y fabricante, mucho más directa y las inversiones empresariales son mucho menores).

Tamaño mínimo 0.4 m, esto viene dado porque la longitud de onda de la luz utilizada para las máscaras oscila entre 0.3 y 0.7 m m. y se producen fenómenos de difracción óptica, proceso que impide la buena realización fotolitográfica.

-Los procesos de introducción de dopantes ha pasado por 4 tipos de fabricación básicamente:

Aleación:

El dopante que queremos introducir se pone en contacto con el semiconductor, a los cuales se le pone a una temperatura alta para poderse producir la aleación.

El dispositivo ocupa un 1% del espesor total de la oblea, por tanto hay un 99% que no se aprovecha, esta zona "muerta" además da problemas de funcionamiento del dispositivo.

.-Problemas:

*No se controla la introducción de dopantes

*Se tiene que reducir la zona muerta.

Difusión:

La física del proceso es la misma, que en el caso anterior, pero tenemos un control mucho mayor sobre él. En este caso el dopante está en forma gaseosa, para introducirlo en las zonas que queremos dopar.

.-Problemas:

*Interconexiones entre los dispositivos.

*Sigue existiendo zonas muertas.

*El control debería ser mayor sobre las zonas a dopar.

Difusión Planar-Epitaxial:

Partimos de un cristal fuertemente dopado, al cual se le hace crecer una capa epitaxial, de semiconductor con un dopado menor. Posteriormente se oxida el Si, de forma que obtenemos SiO2. Se abren huecos en el óxido para que las impurezas entren donde nosotros queremos:

El dopante se introduce en todas las direcciones de forma que no es igual el área de la superficie a la proyectada. Con este proceso hemos resuelto el problema de la zona muerta.

.-Problemas:

*Difusión lateral

*Si las dimensiones se reducen la difusión lateral puede hacer que tengamos una unión en los dispositivos.

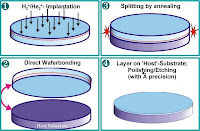

Implantación Iónica:

El proceso es totalmente análogo al anterior pero cambiamos la tecnología utilizada en la introducción de los dopantes. Las impurezas se aceleran utilizando potenciales de 100000 V. Pudiendo controlar perfectamente variando la energía de los iones los lugares donde queremos introducirlos.

Crecimiento de Cristales

El primer problema que tenemos es conseguir Si con un alto grado de pureza, para poder fabricar Si cristalino. La densidad efectiva de átomos debe ser 10 23, para el purificado se hace reaccionar con clorhídrico en fase vapor, y después de varias reacciones (Destilación fraccionaria), obtenemos lo que se llama Si electrónico. Una vez conseguido esto ya podemos darle una estructura cristalina.

Método Czochralski :

En una atmósfera controlada e inerte, tenemos una cubeta de grafito o cuarzo (que funden a temperaturas 3000 ºC En la cubeta se introduce Si electrónico . El cilindro está rodeado de una bobina de alta frecuencia y alta

corriente, con esto se funde el Si (1240 ºC). Se introduce en el Si fundido una pértiga con una semilla de Si cristalino, el cual por capilaridad se une a la semilla, formándose Si cristalino alrededor de la semilla, de forma que tirando y girando la pértiga hacemos crecer el cristal. (5 a 6 pulgadas de diámetro).

Este método así realizado tiene un problema y es que las paredes de cuarzo o de grafito, introducen impurezas en el Si cristalino que se forma, porque al estar toda la cubeta a una temperatura alta se producen deterioros en esta. Para evitar esto se va utilizar el método de la zona flotante, en el cual la bobina no está en todo el cristal sino únicamente en una zona muy concreta alrededor de la semilla, esta bobina es móvil y según movemos la semilla la bobina la acompaña. El problema que tenemos ahora es que hay un alto número de dislocaciones debido al gradiente térmico.

El lingote de Si cristalino se corta en obleas, perdiéndose en el proceso la mitad del Si. Luego viene un proceso de redondeado y de pulido.

Procesos de Dopado

Difusión :

La introducción de dopantes en Si como se produce a partir de una fase gaseosa, lo cual hace que la ley que rige el proceso sea la siguiente :

Donde C es la concentración de impurezas, y D el coeficiente de Difusión, que depende del material del dopante. Las temperaturas a las cuales nos movemos para estos procesos rondan los 1000ºC. Hay un problema en los procesos de difusión y es que la temperatura hay que controlarla muy bien, dado que sino la concentración de impurezas puede variar bastante en tan solo 50 ºC. Tenemos un límite de solubilidad que es la máxima concentración del dopante que admite el Si.

-Etapas del proceso de dopado por difusión :

1ª. Etapa :

Predepósito:

Se genera una presión de vapor de la impureza que queremos introducir.

Condiciones de contorno de la ec. de difusión.

C(0,t)=C s ; Ct)=0 ; C(x,0)=0

Donde la solución para la ecuación de difusión es

donde la función erf c (x) cumple las siguientes propiedades :

erf c(x)=1-erf(x)

donde erf(0)=0 y erf ( ¥ )

Por tanto el número de impurezas introducidas, por cm 2 en tiempo son :

2ª Etapa :

Redistribución

Una vez situadas las impurezas en el proceso de predepósito, retiramos la fuente gaseosa que contiene el dopante. Posteriormente estas impurezas se redistribuyen durante un tiempo y a una temperatura determinada.

Por tanto las condiciones de contorno para nuestra ecuación de difusión son las siguientes :

Donde D 2=Coef. de difusión a la temperatura de redistribución, y t 2 el tiempo de redistribución. Se puede determinar la posición de una unión cuyo dopado ha sido realizado por difusión.

La posición nos la da la siguiente ecuación :

N A(x j,t)=N D

donde N A(x j,t) es :

N A(x j,t)= si ha habido predepósito

N A(x j,t)= si ha habido redistribución.

Ej . : Sobre una oblea de n-Si (N D=10 15 cm -3) se predeposita Boro con los siguientes datos : C s=10 18 cm -3 ; T 1=1000 ºC, t 1= 5 min. Después de este proceso se redistribuyen a T 2=1200 ºC durante t 2=2 horas. Encontrar :

- El perfil de Impurezas

- Posición de la unión.

Implantación Iónica :

Es un proceso de alto vacío en el cual introducimos dopantes en un sólido a partir de haces de iones, fuertemente acelerado, de la impurezas que queramos usar.

-Hay procesos de colisión , con lo cual hay desviaciones en los iones. También se produce el efecto contrario que es la rotura de los átomos de la red en la zona de impacto, generando vacantes en la estructura cristalina.

-El perfil de dopado de las impurezas dentro del cristal cumple una ley gaussiana de probabilidad, de tener una concentración en un lugar geométrico x,y,z.

-Una vez obtenido el perfil hay que reordenar la red mediante un recocido para que los iones de la red se coloquen en sus posiciones originales, y de vez en cuando un ion implantado se coloque en la posición de un ion de la red. (Si la concentración de dopantes fuera análoga a la del semiconductor tendríamos una aleación.

-Ventajas de la Implantación Iónica :

Separación de masas : No tenemos dopantes que no deseamos, dado que separamos muy bien los iones, como luego se verá en el montaje del sistema.

Como tenemos un entorno de vacío, tenemos ausencia de contaminantes.

Como el proceso lo realizamos a baja temperatura evitamos la redistribución de las impurezas, cosa que nos haría perder nuestros perfiles de dopado, y mantenerlos todo lo abruptos que queramos.

-Inconvenientes de la Implantación Iónica :

Dañado : El ion implantado destruye la red cristalina, y por tanto necesitamos recocidos de recristalización (RTA). Esto tiene un problema y es que pueden producir redistribuciones en las impurezas, esto no ocurre si el tiempo del recocido y el coeficiente de Difusión de las impurezas dentro del semiconductor no es demasiado alto. Por eso se utilizan hornos que alcanzan alta temperatura en un intervalo de tiempo muy corto.

Costo del equipamiento.

Oxidación Térmica, Litografía y Grabado

Oxidación Térmica:

Consiste en el crecimiento de una capa de SiO 2 sobre una superficie de Si a expensas de este.

Hay dos tipos de hacer este óxido, en atmósfera seca O 2 o húmeda (H 20) a una temperatura elevada ( ~1000 ºC)

La oxidación seca es bastante lenta pero produce un óxido de excelente calidad, que es muy usado en las tecnologías MOS para el óxido de puerta.

La oxidación húmeda es bastante más rápida pero produce un óxido de mucha peor calidad, con porosidades, el cual solo sirve para procesos de enmascaramiento.

Aplicaciones del SiO 2 :

Máscara de protección para procesos de dopado=>Dopados Selectivos.(0.3 m m de espesor aproximado)

Óxido de puerta en estructuras MOS

Óxido de Aislamiento en tecnologías LOCOS (Local Oxidation Silicon )

Pasivación eléctrica de superficies

Modelo Elemental del Proceso de Oxidación :

La atmósfera oxidante se satura de manera que la concentración de oxidante en la superficie de SiO 2 es la de máxima solubilidad N 0.

El oxidante se difunde a través del SiO 2 formado y llega a la interfase SiO 2 -Si en concentración N 1<>

Flujo de oxidante a través del óxido :

donde D es el coeficiente de Difusión en SiO 2 del O 2 y del H 2O.

El flujo de oxidante que llega a la interfase SiO 2-Si es el siguiente :

F 2=kN 1, donde k es la velocidad de reacción superficial.

La situación estacionaria la tenemos cuando el SiO 2 no es fuente ni sumidero de oxidante por tanto estamos en un proceso de equilibrio :

F 1=F 2=F

En esta situación tenemos que el flujo n.

Tenemos por tanto que la velocidad de crecimiento del óxido con la condición inicial x 0(t=0)=x i (~40 Å)

A=2D/k

B=2DN 0/N 1

t =(x i 2+Ax i)/B

Podemos observar dos resultados principales de la expresión obtenida que son :

-A tiempos cortos de oxidación, el proceso viene limitado por la velocidad de oxidación superficial del Si.

-A tiempos largos de Oxidación, el proceso viene limitado por la difusión de oxidante a través del SiO 2 .

Ej. : Demostrar utilizando la expresión obtenida las dos afirmaciones anteriores.

Litografía y Grabado

Se refieren a los procesos de transferencia de los motivos, que dan lugar al circuito integrado, sobre la oblea del semiconductor.

La litografía es la exposición de motivos a través de máscaras convenientemente diseñadas y el Grabado es la eliminación selectiva de óxidos, metales, etc

Estos procesos son los que nos marcan la tecnología en la construcción de C.I., y por tanto una avance en estos procesos permite una evolución en la tecnología de integración.

El proceso litográfico consta de los siguientes pasos :

-Una vez generado el óxido del Si, sobre el semiconductor, colocamos una capa de Fotorresina sobre el óxido.

-Una vez hecho, hacemos pasar luz (UVA), a través de una Máscara, el cual se proyecta sobre la fotorresina.

- La fotorresina ha quedado impresionada por la proyección hecha en el proceso anterior. Y la introducimos en un compuesto el cual elimina la zona impresionada (Positivo), o la que no lo está (Negativo).

El Inversor CMOS

Hoy en día la gran mayoría de los circuitos integrados de Aplicación específica, utilizan tecnología CMOS. La cual se nutre a su vez de los transistores MOS (Metal Óxido Semiconductor), los cuales vamos a empezar estudiando para entender las bases de funcionamiento tanto en el aspecto estático como en el dinámico.

El transistor MOS

Representamos a continuación circuitalmente un transistor MOS de canal n, cuyas conexiones son:

-Puerta G

-Fuente S

-Drenador D

Y sean VG, VS y VD, las diferencias de potencial entre dichas conexiones y el substrato de Si, tipo p sobre cuya superficie se ha integrado el transistor.

El funcionamiento del dispositivo es sencillo:

-Mientras la tensión VG es menor que un valor mínimo,

corriente que circula entre el drenador y la fuente es despreciable.

-En cambio si sobrepasamos el valor mínimo de VG, se crea un canal de inversión tipo n, entre la fuente y el drenador. Si la tensión VD es mayor que VS, circulará una corriente entre ambos que llamamos IDS.

Tenemos que hacer un estudio detallado de la tensión umbral en un punto del canal, que es el valor mínimo de la tensión VG para que la zona de inversión se mantenga dicho punto del canal. Este valor depende de la diferencia de potencial V, entre el punto del canal considerado y el substrato. (Ver figura de la variación de la tensión umbral con (VT, V).

Un resultado importante que podemos obtener es el de la densidad de cargas libres en un punto del canal del MOS. Como ya sabemos la Capacidad de un condensador viene dada por la expresión C=Q/V, viendo que en el transistor MOS entre el contacto metálico y el semiconductor tenemos un condensador, con lo cual aplicando lo antes dicho, podemos deducir que:

s =C ox[VG-VT(V)] (1)

donde C ox es la capacidad por unidad de superficie del condensador formado por la puerta, el óxido y el canal [Faradios/m 2]. Y V es como antes dijimos la diferencia de potencial entre el punto considerado y el substrato.

Vamos a entrar ahora en el Cálculo de la Corriente que pasa por el canal del transistor. Si tomamos como la superficie en la cual vamos a hacer nuestro estudio, como una zona del canal de longitud infinitesimal dx y de anchura W . Aplicando estos datos en la ecuación anterior (1), obtenemos que el valor dQ de cargas libres en el canal son las siguientes:

dQ=dxWC ox[VG-VT(V)]

Sabiendo que el campo Eléctrico en esta zona es igual a :

E=dV/dx

y que la velocidad de desplazamiento de los electrones viene dada por el producto de la movilidad de estos, por el campo Eléctrico aplicado.

v= m n dV/dx

Por tanto como conocemos la velocidad y la distancia que tienen que recorrer podemos calcular el tiempo de tránsito de los electrones.

t=dx/v=(dx) 2/ m n dV (2)

Y por tanto la corriente que atraviesa el canal es la siguiente, y utilizando las ecuaciones.

I= dQ/t

I dx = m n W C ox[VG-VT(V)] dV

Si despreciamos las corrientes de fuga, lo cual nos hace considerar que la corriente a lo largo del canal es la misma. Integramos la anterior relación.

Corriente de Saturación

Todo este proceso es válido siempre que no supere VD el valor VDP. Si tenemos el caso en el cual coinciden estos dos valores, tenemos que la tensión de puerta es igual a la tensión umbral, con lo cual, dicha tensión de puerta no puede mantener los portadores libres en el canal cerca del drenador. Este fenómeno se le conoce con el nombre de Pinch-Off o estrangulamiento del canal. Se produce por tanto una zona de empobrecimiento en la cual no existen portadores libres, y todo aumento en la tensión del drenador cae en esta zona.

El potencial en la zona de canal que aun tiene portadores sigue siendo VDP. Por tanto el potencial en el canal viene dado por la diferencia de potencial entre la fuente y la zona de estrangulamiento (VDP). Si suponemos que la longitud del canal entre la fuente y la zona de estrangulamiento prácticamente no se modifica, podemos considerar que la corriente entre el drenador y la fuente IDS, permanece invariable. Por lo tanto como hay una diferencia de potencial existe un campo eléctrico, de valor :

(VD-VDP)/l

que nos hace conducir los electrones al drenador.

Por lo tanto cuando VD>VDP la corriente IDS toma un valor constante :

IDSsat= m n . C ox (W/L) Ssat

Donde Ssat es la superficie representada en la siguiente figura :

Podemos obtener la curva IDS en función de VDS, y ver que se comporta como una resistencia, función de la tensión VD.

1/R=dIDS/dVD= m n . C ox (W/L) dS/dVD

El valor de dS/dVD se deduce directamente en la siguiente figura :

dS=hdVD

Con lo cual dS/dVD=h, con lo cual la resistencia es proporcional a 1/h, según aumenta VD disminuye h, y por tanto aumenta la resistencia, hasta que alcanza un valor infinito cuando el transistor esta saturado. Con lo cual la curva IDS, VDS (VD-VS), para un valor fijo de las tensiones VG y VS.

El Transistor MOS de Canal P

El estudio del transistor MOS tipo P es análogo al hecho en el caso de los tipo N. Al igual que antes los potenciales se definen en función del substrato que utilizamos en este caso tipo N. En este caso como ya se podía esperar las tensiones VG, VS y VD son negativas. Por tanto el proceso de funcionamiento es el siguiente cuando tenemos una tensión VG menor que la tensión VT (Que también es negativa), un canal tipo P aparece entre el drenador y la fuente, si además hay una diferencia de potencial entre el drenador y la fuente, aparece una corriente ISD entre estos dos puntos. Tanto en el transistor de canal N como en el de canal P, los portadores van siempre del drenador a la fuente, aunque en el caso de las corriente van en sentidos contrarios. (n=IDS y p=ISD). El símbolo del transistor p lo tenemos a continuación, junto con su estructura física :

Las expresiones son análogas que en el caso anterior, pero donde antes teníamos la movilidad m n ahora tenemos la de los huecos m p .

Por tanto la corriente ISD es la siguiente :

ISD= m p . C ox (W/L) S

Siendo S la superficie representada en la siguiente figura :

Si VD(< ó =)VDP, entonces el transistor está saturado, con lo cual la corriente es :

ISD sat= m p . C ox (W/L) S sat

Donde la superficie S sat viene dada en la siguiente figura :

El Inversor :

Vamos a estudiar ahora el elemento más importante dentro de la microelectrónica actual como es el inversor CMOS, cuyo esquema se representa en la siguiente figura. Como se ve se tiene que contar con dos substratos :

- Uno tipo p, conectado a VSS voltios, cobre la cual se pone el transistor de canal n

- Otro tipo n, conectado a VSS+VDD, sobre cuya superficie se integra el transistor de canal p.

Funcionamiento Estático :

Ahora vamos a suponer que todas las tensiones se miden con respecto a la tensión VSS, que la hacemos 0 voltios. Dentro de las tensiones umbrales de los dos transistores , supondremos a su vez que:

VT0n<>

Supondremos también que en el funcionamiento estático la corriente de salida será nula:

IOUT=0 A

Que corresponde al caso en que a la salida tengamos un condensador, y que esté en estado estable.(Ver siguiente figura)

Vamos a ver los posibles casos que se pueden dar en esta configuración:

- Si VIN>VDD+VT0p, entonces podemos ver ahora el canal p, es el que está en corte. Por tanto ahora la tensión de salida debe ser 0 para que no pase corriente por el transistor de canal n, y por tanto IOUT=0.

- Tenemos otro caso en el cual, se pude demostrar que hay un valor de Vinv ,tal que la salida pueda ser cualquiera comprendida entre VDPn, y VDPp, este valor es el que define dos superficies de integración Sp y Sn, tales que:

m n . C ox (W n/L n) Sn= m p . C ox (W p/L p) Sp

Con lo cual los dos transistores dan la misma corriente, y por tanto a la salida tenemos que de nuevo IOUT=0

-Por tanto la curva de transferencia del inversor CMOS, viene dada en la siguiente figura:

-Como se puede ver en las expresiones anteriores la tensión V inv depende del valor relativo de las dimensiones de los dos transistores:

(W n/L n)/ (W p/L p)

También, podemos ver la corriente Interna en función de la tensión de entrada Vin. Como podemos ver solo hay paso de corriente en el intervalo del cambio de on-off, que es cuando tenemos una IDS.

El valor máximo viene dado por los valores de las corrientes IDSn e IDSp, calculadas con anterioridad.

Funcionamiento Dinámico

Normalmente en un circuito integrado las salidas y las entradas de los inversores se conectan a otros inversores, o a otras puertas lógicas. Entonces para hacer el estudio dinámico, debemos hacer algunas modelizaciones. La admitancia de entrada se aproxima con un condensador de valor constante. Por tanto despreciamos:

La corriente de entrada continua de los transistores.

La variación de la capacidad de entrada con la tensión de entrada.

Por tanto el cálculo de los tiempos de salida lo hacemos a partir del siguiente esquema:

a)Tiempo de Subida:

Suponemos que VIN=VSS y que la tensión de salida es V voltios. En las siguientes figuras vemos el significado de los valores Sp(V) y Sn(V).

En este estado, sabemos que el transistor de canal n está en corte, y por tanto el único que conduce es el p. Con lo cual la corriente que pasa por el CMOS, es la siguiente :

I = m p . C ox (W p/L p) Sp(V)

Y recordando la relación vista :

dt=dQ/I=CLdV/[ m p . C ox (W p/L p) Sp]

Por tanto el tiempo necesario para pasar de una tensión V L a una V H es el siguiente :

t=[ CL/[ m p . C ox (W p/L p)] Análogamente podemos calcular el tiempo de bajada del CMOS, en este caso es el transistor de canal p el que está en corte, y el n conduce, con lo cual el tiempo que nos sale es :

t= CL/[ m n . C ox (W n/L n)] Consumo :

Como pudimos observar cuando vimos la corriente interna que pasaba por el CMOS, era en el momento de la conmutación, cuando el paso de corriente era mayor. Por tanto como sabemos la potencia consumida es función de la intensidad, con lo cual tendremos un mayor gasto de potencia, cuando tenemos conmutaciones (Pasos de altas a bajas, y viceversa)